I want to know how to enable the $display/$error output defined in the assert property. I don't see it output in the log file.

Here is the system Verilog code:

##########start of sv code##################

module sv_as_micbiasamp_ibias5uA (

input real as_micbiasamp_ibias5uA,

output real as_micbias

);

localparam micbias_min5000 = 4500e-9;

localparam micbias_max5000 = 5500e-9;

// assert (as_micbiasamp_ibias5uA == 5e-6) $display ("OK. as_micbiasamp_ibias5uA equals 5uA");

wire micbias_ready = (as_micbiasamp_ibias5uA >= micbias_min5000) && (as_micbiasamp_ibias5uA <= micbias_max5000);

wire #10 up = micbias_ready;

property bias_current_micbias (tick, sig, lower, upper);

@(posedge tick) (lower < sig && sig < upper);

endproperty

CHK_MICBIAS_MIC_BIAS_5U: assert property(bias_current_micbias(up, as_micbiasamp_ibias5uA , 450e-8, 550e-8)) $display ("OK. current is within 5uA limit");

else $error ("MICBIAS error. Bias current micbias 5uA is not within limits");

always @*

if (up) begin

assign as_micbias = 1;

$display ("where this is displayed. OK");

end

else begin

assign as_micbias = 0;

$error ("where this is displayed. ERROR");

end

endmodule

########end of sv code###########

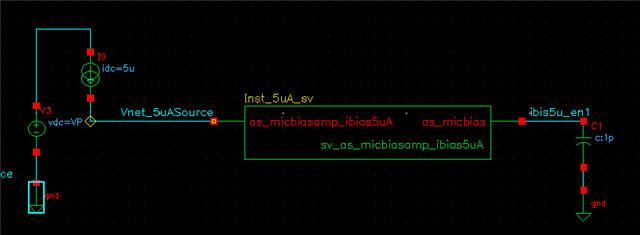

here is how the test bench looks like. I also have the ams config file and interface element setup properly for the net of Vnet_5uASource. The simulation can run correctly.

![]()

I have test bench to report if the analog current into the systemverilog module is pithing 4.5uA or 5.5uA.

The $display and $error defined inside the property bias_current_micbias will not give any log output. But the $display and $error defined in the always @* block will correctly output to the log or SimVision console.

I want to see the below log displayed. Is there a setting will enable this feature?

$display ("OK. current is within 5uA limit");

$error ("MICBIAS error. Bias current micbias 5uA is not within limits");

##############example of $display and $error output ############

![]()

![]()

#############end of the output of $display and $error#################

community.cadence.com/.../test_5F00_AMS_5F00_log_5F00_error_5F00_assert_5F00_property.log

![]()