I started recently with SystemVerilog (lets say Verilog in general) and I am trying to create a "task()".

I am using the Virtuoso/Xcelium AMS environment and want to generate a pulse with configurable length.

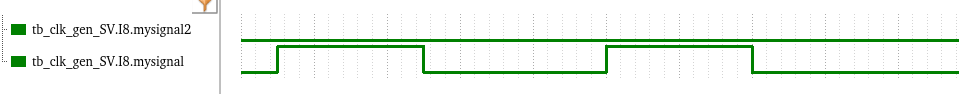

I am using 2 internal signals in the module "mysignal" and "mysignal2".

"mysignal" is directly assigned with a value inside the task().

"mysignal2" shall get the value from the task() output signal assignment.

Here my code:

`timescale 1 ns / 1 ns

module clk_gen_SV_stim (GEN_ADCCLK, GEN_CLKGEN_ADC_RATE,

GEN_CLKGEN_BYPASS, GEN_CLKGEN_DIV_F, GEN_CLKGEN_EN

);

output logic GEN_CLKGEN_DIV_F;

output logic GEN_CLKGEN_ADC_RATE;

output logic GEN_CLKGEN_EN = 1'b0;

output logic GEN_ADCCLK;

output logic GEN_CLKGEN_BYPASS;

logic mysignal = 1'b0;

logic mysignal2 = 1'b0;

// task

task pulse( input time length, output intsig);

mysignal = 1'b1;

intsig = 1'b1;

$display("intsig =%b at %t",intsig, $time() );

#length

mysignal = 1'b0;

intsig = 1'b0;

//GEN_CLKGEN_EN = 1'b0;

$display("intsig =%b at %t",intsig, $time() );

endtask : pulse

//start with state 0

initial begin

#5ns

pulse(.length(20ns), .intsig(mysignal2)); //call with argument mapping

#25ns

pulse(20ns, mysignal2); //call with positional argument

end

endmodule

The problem is, that "mysignal2" never changes its value.

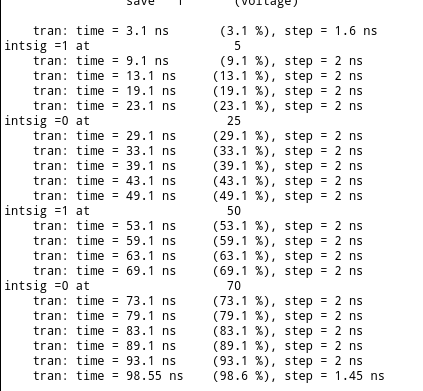

But internally in the task() the local "intsig" is assigned properly:

Does anyone know why, and whats wrong with the "mysignal2" assignment ?

Ar do I have wrong expectations on "mysignal2" behaviour ?